# LC<sup>2</sup>MOS Dual 12-Bit Serial DACPORT®

# AD7249

#### FEATURES

Two 12-Bit CMOS DAC Channels with On-Chip Voltage Reference Output Amplifiers Three Selectable Output Ranges per Channel -5 V to +5 V, 0 V to +5 V, 0 V to +10 V Serial Interface 125 kHz DAC Update Rate Small Size: 16-Lead DIP or SOIC Low Power Dissipation

#### APPLICATIONS Process Control

Industrial Automation Digital Signal Processing Systems Input/Output Ports

#### **GENERAL DESCRIPTION**

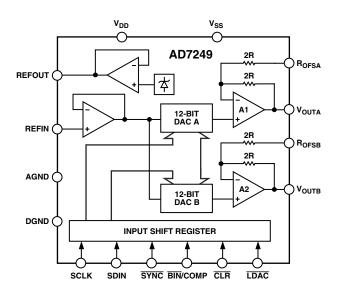

The AD7249 DACPORT contains a pair of 12-bit, voltageoutput, digital-to-analog converters with output amplifiers and Zener voltage reference on a monolithic CMOS chip. No external trims are required to achieve full specified performance.

The output amplifiers are capable of developing +10 V across a 2 k $\Omega$  load. The output voltage ranges with single supply operation are 0 V to +5 V or 0 V to +10 V, while an additional bipolar  $\pm 5$  V output range is available with dual supplies. The ranges are selected using the internal gain resistor.

Interfacing to the AD7249 is serial, minimizing pin count and allowing a small package size. Standard control signals allow interfacing to most DSP processors and microcontrollers. The data stream consists of 16 bits, DB15 to DB13 are don't care bits, the 13th bit (DB12) is used as the channel select bit and the remaining 12 bits (DB11 to DB0) contain the data to update the DAC. The 16-bit data word is clocked into the input register on each falling SCLK edge.

The data format is natural binary in both unipolar ranges, while either offset binary or twos complement format may be selected in the bipolar range. A  $\overline{CLR}$  function is provided which sets the output to 0 V in both unipolar ranges and in the twos complement bipolar range, while with offset binary data format, the output is set to –REFIN. This function is useful as a power-on reset as it allows the outputs to be set to a known voltage level.

#### FUNCTIONAL BLOCK DIAGRAM

The AD7249 features a serial interface which allows easy connection to both microcomputers and 16-bit digital signal processors with serial ports. The serial data may be applied at rates up to 2 MHz allowing a DAC update rate of 125 kHz.

The AD7249 is fabricated on linear compatible CMOS ( $LC^2MOS$ ), an advanced, mixed technology process. It is packaged in 16-lead DIP and 16-lead SOIC packages.

#### **PRODUCT HIGHLIGHTS**

- 1. Two complete 12-bit DACPORTs The AD7249 contains two complete voltage output, 12-bit DACs in both 16-lead DIP and SOIC packages.

- 2. Single or dual supply operation

- 3. Minimum 3-wire interface to most DSP processors

- 4. DAC update rate-125 kHz

DACPORT is a registered trademark of Analog Devices, Inc.

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

$\begin{array}{l} \textbf{AD7249} \textbf{\_SPECIFICATIONS} \\ +5 \text{ V}, \text{ } \text{R}_{L} = 2 \text{ } \text{k} \Omega, \text{ } \text{C}_{L} = 100 \text{ } \text{pF} \text{ to AGND. All specifications } \text{T}_{\text{MIN}} \text{ to } \text{T}_{\text{MAX}} \text{ unless otherwise noted.} \end{array}$

| Parameter                                                                                                                                                                            | A Version <sup>2</sup>                  | B Version <sup>2</sup>                 | S Version <sup>2</sup>                 | Unit                           | Test Conditions/Comments                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                                                                                                                                                   |                                         |                                        |                                        |                                |                                                                                       |

| Resolution                                                                                                                                                                           | 12                                      | 12                                     | 12                                     | Bits                           |                                                                                       |

| Relative Accuracy <sup>3</sup>                                                                                                                                                       | ±1                                      | $\pm 1/2$                              | $\pm 1$                                | LSB max                        |                                                                                       |

| Differential Nonlinearity <sup>3</sup>                                                                                                                                               | ±0.9                                    | $\pm 0.9$                              | $\pm 0.9$                              | LSB max                        | Guaranteed Monotonic                                                                  |

| Unipolar Offset Error <sup>3</sup>                                                                                                                                                   | ±5                                      | ±5                                     | $\pm 6.9$                              | LSB max                        | $V_{SS} = 0 \text{ V or } -12 \text{ V to } -15 \text{ V}^1; \text{ DAC}$             |

| Olipolar Oliset Error                                                                                                                                                                | <u> </u>                                | <u>+</u> )                             | ±0                                     |                                | Latch Contents All 0s                                                                 |

| Bipolar Zero Error <sup>3</sup>                                                                                                                                                      | ±6                                      | ±5                                     | ±7                                     | LSB max                        | $V_{SS} = -12 \text{ V to } -15 \text{ V}^1$<br>DAC Latch Contents All 0s             |

| Full-Scale Error <sup>3, 4</sup>                                                                                                                                                     | ±6                                      | ±6                                     | ±7                                     | LSB max                        |                                                                                       |

| Full-Scale Temperature Coefficient                                                                                                                                                   | ±5                                      | ±5                                     | ±5                                     | ppm of FSR/°C typ              |                                                                                       |

| REFERENCE OUTPUT<br>REFOUT<br>Reference Temperature Coefficient<br>Reference Load Change                                                                                             | 4.95/5.05<br>±25                        | 4.95/5.05<br>±25                       | 4.95/5.05<br>±30                       | V min/V max<br>ppm/°C typ      |                                                                                       |

| $(\Delta V_{REFOUT} \text{ vs. } I_L)$                                                                                                                                               | -1                                      | -1                                     | -1                                     | mV max                         | Reference Load Current ( $I_L$ )<br>Change (0 $\mu$ A–100 $\mu$ A)                    |

| REFERENCE INPUT<br>Reference Input Range, REFIN<br>Input Current                                                                                                                     | 4.95/5.05<br>5                          | 4.95/5.05<br>5                         | 4.95/5.05<br>5                         | V min/V max<br>μA max          | 5 V ± 1%                                                                              |

| DIGITAL INPUTS                                                                                                                                                                       |                                         |                                        |                                        |                                |                                                                                       |

| Input High Voltage, V <sub>INH</sub>                                                                                                                                                 | 2.4                                     | 2.4                                    | 2.4                                    | V min                          |                                                                                       |

|                                                                                                                                                                                      | 2.4                                     | 2.4                                    | 2.4                                    |                                |                                                                                       |

| Input Low Voltage, V <sub>INL</sub><br>Input Current                                                                                                                                 | 0.8                                     | 0.8                                    | 0.8                                    | V max                          |                                                                                       |

|                                                                                                                                                                                      | +1                                      | ±1                                     | ± 1                                    | µA max                         | $V_{\rm IN} = 0$ V to $V_{\rm DD}$                                                    |

| I <sub>IN</sub><br>Input Capacitance <sup>5</sup>                                                                                                                                    | $\begin{array}{c} \pm 1\\ 8\end{array}$ | $\frac{1}{8}$                          | $\frac{\pm 1}{8}$                      | pF max                         | $\mathbf{v}_{\rm IN} = 0 \mathbf{v} \mathbf{t} 0 \mathbf{v}_{\rm DD}$                 |

| ANALOG OUTPUTS                                                                                                                                                                       |                                         |                                        |                                        | F                              |                                                                                       |

| ANALOG OUTPOTS<br>Output Range Resistor,<br>R <sub>OFSA</sub> & R <sub>OFSB</sub><br>Output Voltage Ranges <sup>6</sup><br>Output Voltage Ranges <sup>6</sup><br>DC Output Impedance | 15/30<br>+5, +10<br>+5, +10, ±5<br>0.5  | 15/30<br>+5, +10<br>+5, +10, ±5<br>0.5 | 15/30<br>+5, +10<br>+5, +10, ±5<br>0.5 | kΩ min/ max<br>V<br>V<br>Ω typ | Single Supply; V <sub>SS</sub> = 0 V<br>Dual Supply; V <sub>SS</sub> = -12 V or -15 V |

| AC CHARACTERISTICS <sup>5</sup>                                                                                                                                                      |                                         |                                        |                                        |                                |                                                                                       |

| Voltage Output Settling-Time                                                                                                                                                         |                                         |                                        |                                        |                                | Settling Time to Within $\pm 1/2$ LSB of Final Value                                  |

| Positive Full-Scale Change                                                                                                                                                           | 10                                      | 10                                     | 10                                     | µs max                         | Typically 3 µs                                                                        |

| Negative Full-Scale Change                                                                                                                                                           | 10                                      | 10                                     | 10                                     | µs max                         | Typically 5 µs                                                                        |

| Digital-to-Analog Glitch Impulse <sup>3</sup>                                                                                                                                        | 30                                      | 30                                     | 30                                     | nV secs typ                    | 1 LSB Change Around<br>Major Carry                                                    |

| Digital Feedthrough <sup>3</sup>                                                                                                                                                     | 10                                      | 10                                     | 10                                     | nV secs typ                    |                                                                                       |

| Digital Crosstalk <sup>3</sup>                                                                                                                                                       | 10                                      | 10                                     | 10                                     | nV secs typ                    |                                                                                       |

| POWER REQUIREMENTS                                                                                                                                                                   |                                         |                                        |                                        |                                |                                                                                       |

| V <sub>DD</sub> Range                                                                                                                                                                | +10.8/+16.5                             | +11.4/+15.75                           | +11.4/+15.75                           | V min/V max                    | For Specified Performance Unless<br>Otherwise Stated                                  |

| V <sub>SS</sub> Range (Dual Supplies)                                                                                                                                                | -10.8/-16.5                             | -11.4/-15.75                           | -11.4/-15.75                           | V min/V max                    | For Specified Performance Unless<br>Otherwise Stated                                  |

| I <sub>DD</sub>                                                                                                                                                                      | 15                                      | 15                                     | 15                                     | mA max                         | Output Unloaded; Typically 11 mA                                                      |

| I <sub>ss</sub> (Dual Supplies)                                                                                                                                                      | 5                                       | 5                                      | 5                                      | mA max                         | Output Unloaded; Typically 3 mA                                                       |

| 155 (Duai Supplies)                                                                                                                                                                  | ,                                       | ر<br>۱                                 | `                                      | 111/1 Шал                      | Surpur Onioaucu, Typicany 5 IIIA                                                      |

NOTES

<sup>1</sup>Power supply tolerance, A Version:  $\pm 10\%$ ; B, S Versions:  $\pm 5\%$ .

<sup>2</sup>Temperature ranges are as follows: A, B Versions: -40°C to +85°C; S Version: -55°C to +125°C.

<sup>3</sup>See Terminology.

<sup>4</sup>Measured with respect to REFIN and includes unipolar/bipolar offset error.

<sup>5</sup>Guaranteed by design not production tested.

$^60$  V to 10 V output range available only with  $V_{\rm DD} \geq 14.25$  V.

Specifications subject to change without notice.

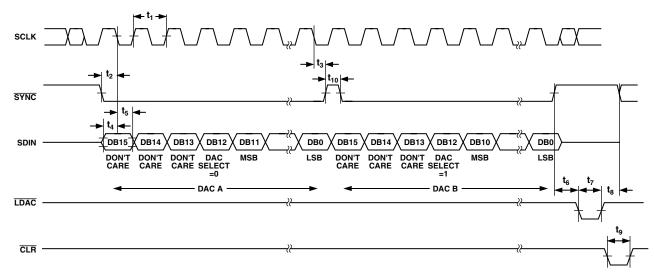

# **TIMING CHARACTERISTICS**<sup>1, 2</sup> $\begin{pmatrix} V_{DD} = +12 \text{ V to } +15 \text{ V}, {}^{3} \text{ V}_{SS} = 0 \text{ V or } -12 \text{ V to } -15 \text{ V}, {}^{3} \text{ AGND} = \text{DGND} = 0 \text{ V}, \text{ R}_{L} = 2 \text{ k}\Omega, \text{ C}_{L} = 100 \text{ pF.}$ All specifications T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted.)

| Parameter       | Limit at T <sub>MIN</sub> to T <sub>MAX</sub><br>(All Versions) | Unit   | Conditions/Comments                                           |

|-----------------|-----------------------------------------------------------------|--------|---------------------------------------------------------------|

| $t_{1}^{4}$     | 200                                                             | ns min | SCLK Cycle Time                                               |

| t <sub>2</sub>  | 15                                                              | ns min | SYNC to SCLK Falling Edge Setup Time                          |

| t <sub>3</sub>  | 50                                                              | ns min | SYNC to SCLK Hold Time                                        |

| t <sub>4</sub>  | 0                                                               | ns min | Data Setup Time                                               |

| t <sub>5</sub>  | 150                                                             | ns min | Data Hold Time                                                |

| t <sub>6</sub>  | 0                                                               | ns min | $\overline{\text{SYNC}}$ High to $\overline{\text{LDAC}}$ Low |

| t <sub>7</sub>  | 20                                                              | ns min | LDAC Pulsewidth                                               |

| t <sub>8</sub>  | 0                                                               | ns min | $\overline{\text{LDAC}}$ High to $\overline{\text{SYNC}}$ Low |

| t <sub>9</sub>  | 50                                                              | ns min | CLR Pulsewidth                                                |

| t <sub>10</sub> | 20                                                              | ns min | SYNC High Time                                                |

NOTES

<sup>1</sup>Timing specifications guaranteed by design not production tested. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

<sup>2</sup>See Figure 8.

<sup>3</sup>Power supply tolerance, A Version: ±10%; B, S Versions: ±5%.

<sup>4</sup>SCLK Mark/Space Ratio range is 45/55 to 55/45.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> to AGND, DGND                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{OUTA, B}^2$ to AGND $V_{SS} - 0.3$ V to $V_{DD} + 0.3$ V                                                                             |

| REFOUT to AGND 0 V to V <sub>DD</sub>                                                                                                    |

| <b>REFIN</b> to AGND $\dots \dots \dots$ |

| Digital Inputs to DGND $\dots -0.3$ V to V <sub>DD</sub> + 0.3 V                                                                         |

| Operating Temperature Range                                                                                                              |

| Industrial (A, B Versions) $\dots -40^{\circ}$ C to $+85^{\circ}$ C                                                                      |

| Extended (S Version)                                                                                                                     |

| Junction Temperature                                                                                                                     |

| Storage Temperature Range65°C to +150°C                                                                                                  |

| Power Dissipation Plastic DIP                                                                                                            |

| $\theta_{IA}$ Thermal Impedance+117°C/W                                                                                                  |

| Lead Temperature (Soldering, 10 secs) +300°C                                                                                             |

| Power Dissipation, Cerdip                    |

|----------------------------------------------|

| $\theta_{JA}$ Thermal Impedance              |

| Lead Temperature (Soldering, 10 secs) +300°C |

| Power Dissipation, SOIC                      |

| $\theta_{JA}$ Thermal Impedance              |

| Lead Temperature (Soldering)                 |

| Vapor Phase (60 secs) +215°C                 |

| Infrared (15 secs) +220°C                    |

|                                              |

NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one Absolute Maximum Rating may be applied at any time.

<sup>2</sup>The outputs may be shorted to voltages in this range provided the power dissipation of the package is not exceeded.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7249 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

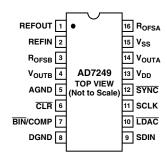

| Pin | Mnemonic          | Description                                                                                                                                                                                                                                                                                                          |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | REFOUT            | Voltage Reference Output. The internal 5 V analog reference is provided at this pin. To operate the part using its internal reference, REFOUT should be connected to REFIN.                                                                                                                                          |

| 2   | REFIN             | Voltage Reference Input. It is internally buffered before being applied to both DACs. The nominal reference voltage for specified operation of the AD7249 is 5 V.                                                                                                                                                    |

| 3   | R <sub>OFSB</sub> | Output Offset Resistor for the amplifier of DAC B. It is connected to $V_{OUTB}$ for the +5 V range, to AGND for the +10 V range and to REFIN for the -5 V to +5 V range.                                                                                                                                            |

| 4   | V <sub>outb</sub> | Analog Output Voltage of DAC B. This is the buffer amplifier output voltage. Three different output voltage ranges can be chosen: $0 V$ to $+5 V$ , $0 V$ to $+10 V$ and $-5 V$ to $+5 V$ .                                                                                                                          |

| 5   | AGND              | Analog Ground. Ground reference for all analog circuitry.                                                                                                                                                                                                                                                            |

| 6   | CLR               | Clear, Logic Input. Taking this input low clears both DACs. It sets $V_{OUTA}$ and $V_{OUTB}$ to 0 V in both unipolar ranges and the twos complement bipolar range and to –REFIN in the offset binary bipolar range.                                                                                                 |

| 7   | BIN/COMP          | Logic Input. This input selects the data format to be either binary or twos complement. In both unipolar ranges natural binary format is selected by connecting this input to a Logic "0". In the bipolar configuration offset binary format is selected with a Logic "0" while a Logic "1" selects twos complement. |

| 8   | DGND              | Digital Ground. Ground reference for all digital circuitry.                                                                                                                                                                                                                                                          |

| 9   | SDIN              | Serial Data In, Logic Input. The 16-bit serial data word is applied to this input.                                                                                                                                                                                                                                   |

| 10  | LDAC              | Load DAC, Logic Input. Updates both DAC outputs. The DAC outputs are updated on the falling edge of this signal or alternatively if this line is permanently low, an automatic update mode is selected whereby both DACs are updated on the 16th falling SCLK pulse.                                                 |

| 11  | SCLK              | Serial Clock, Logic Input. Data is clocked into the input register on each falling SCLK edge.                                                                                                                                                                                                                        |

| 12  | SYNC              | Data Synchronization Pulse, Logic Input. Taking this input low initializes the internal logic in readiness for a new data word.                                                                                                                                                                                      |

| 13  | V <sub>DD</sub>   | Positive Power Supply.                                                                                                                                                                                                                                                                                               |

| 14  | V <sub>OUTA</sub> | Analog Output Voltage of DAC A. This is the buffer amplifier output voltage. Three different output voltage ranges can be chosen: $0 V$ to $+5 V$ , $0 V$ to $+10 V$ and $-5 V$ to $+5 V$ .                                                                                                                          |

| 15  | V <sub>SS</sub>   | Negative Power Supply (used for the output amplifier only) may be connected to 0 V for single supply operation or $-12$ V to $-15$ V for dual supplies.                                                                                                                                                              |

| 16  | R <sub>OFSA</sub> | Output Offset Resistor for the amplifier of DAC A. It is connected to $V_{OUTA}$ for the +5 V range, to AGND for the +10 V range and to REFIN for the -5 V to +5 V range.                                                                                                                                            |

#### PIN CONFIGURATIONS (DIP and SOIC)

#### **ORDERING GUIDE**

| Model                                                                             | Temperature                                                                             | Relative                                             | Package                              |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------|

|                                                                                   | Range                                                                                   | Accuracy                                             | Option                               |

| AD7249AN<br>AD7249BN<br>AD7249AR<br>AD7249BR<br>AD7249BR<br>AD7249SQ <sup>1</sup> | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-55°C to +125°C | ±1 LSB<br>±1/2 LSB<br>±1 LSB<br>±1/2 LSB<br>±1/2 LSB | N-16<br>N-16<br>R-16<br>R-16<br>Q-16 |

NOTE

$^1\mathrm{Available}$  to /883B processing only. Contact your local sales office for military data sheet.

#### TERMINOLOGY

#### **Bipolar Zero Error**

Bipolar Zero Error is the voltage measured at  $V_{OUT}$  when the DAC is configured for bipolar output and loaded with all 0s (Twos Complement Coding) or with 1000 0000 0000 (Offset Binary Coding). It is due to a combination of offset errors in the DAC, amplifier and mismatch between the internal gain resistors around the amplifier.

#### **Full-Scale Error**

Full-Scale Error is a measure of the output error when the amplifier output is at full scale (for the bipolar output range full scale is either positive or negative full scale). It is measured with respect to the reference input voltage and includes the offset errors.

#### Digital-to-Analog Glitch Impulse

This is the voltage spike that appears at  $V_{OUT}$  when the digital code in the DAC Latch changes, before the output settles to its final value. It is normally specified as the area of the glitch in nV-secs and is measured when the digital code is changed by 1 LSB at the major carry transition (0111 1111 1111 to 1000 0000 0000 or 1000 0000 to 0111 1111 1111).

#### **Digital Feedthrough**

This is a measure of the voltage spike that appears on  $V_{OUT}$  as a result of feedthrough from the digital inputs on the AD7249. It is measured with  $\overline{LDAC}$  held high.

#### **Relative Accuracy (Linearity)**

Relative Accuracy, or endpoint linearity, is a measure of the maximum deviation of the DAC transfer function from a straight line passing through the endpoints of the transfer function. It is measured after allowing for zero and full-scale errors and is expressed in LSBs or as a percentage of full-scale reading.

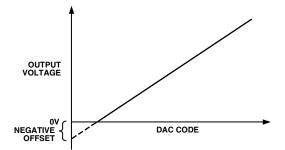

#### Single Supply Linearity and Gain Error

The output amplifier on the AD7249 can have true negative offsets even when the part is operated from a single +15 V supply. However, because the negative supply rail ( $V_{SS}$ ) is 0 V, the output cannot actually go negative. Instead, when the output offset voltage is negative, the output voltage sits at 0 V, resulting in the transfer function shown in Figure 1.

Figure 1. Effect of Negative Offset (Single Supply)

This "knee" is an offset effect, not a linearity error, and the transfer function would have followed the dotted line if the output voltage could have gone negative.

Normally, linearity is measured between zero (all 0s input code) and full scale (all 1s input code) after offset and full scale have been adjusted out or allowed for, but this is not possible in single supply operation if the offset is negative, due to the knee in the transfer function. Instead, linearity of the AD7249 in the unipolar mode is measured between full scale and the lowest code which is guaranteed to produce a positive output voltage. This code is calculated from the maximum specification for negative offset. For the A and B versions, the linearity is measured between Codes 3 and 4095. For the S grade, linearity is measured between Code 5 and Code 4095.

#### **Differential Nonlinearity**

Differential Nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB or less over the operating temperature range ensures monotonicity.

#### **Unipolar Offset Error**

Unipolar Offset Error is the measured output voltage from  $V_{OUT}$  with all zeros loaded into the DAC latch, when the DAC is configured for unipolar output. It is due to a combination of the offset errors in the DAC and output amplifier.

#### CIRCUIT INFORMATION

#### **D/A Section**

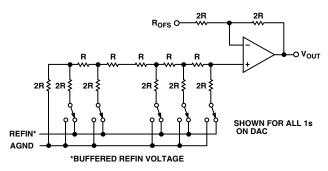

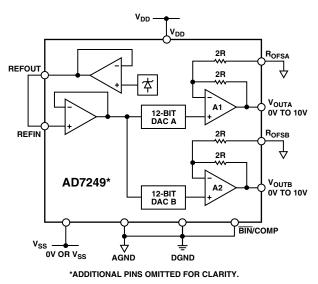

The AD7249 contains two 12-bit voltage-mode D/A converters consisting of highly stable thin film resistors and high-speed NMOS single-pole, double-throw switches. The simplified circuit diagram for the DAC section is shown in Figure 2. The output voltage from the converter has the same polarity as the reference voltage, REFIN, allowing single supply operation.

Figure 2. D/A Simplified Circuit Diagram

#### **Internal Reference**

The AD7249 has an on-chip temperature compensated buried Zener reference which is factory trimmed to  $5 V \pm 50 \text{ mV}$ . The reference voltage is provided at the REFOUT pin. This reference can be used to provide the reference voltage for the D/A converter by connecting the REFOUT pin to the REFIN pin.

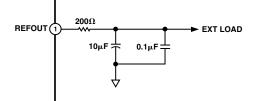

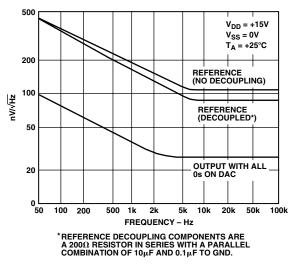

The reference voltage can also be used as a reference for other components and is capable of providing up to 500  $\mu$ A to an external load. The maximum recommended capacitance on REFOUT for normal operation is 50 pF. If the reference output is required to drive a capacitive load greater than 50 pF, then a 200  $\Omega$  resistor should be placed in series with the capacitive load. Figure 3 shows the suggested REF OUT decoupling scheme, a 200  $\Omega$  resistor and the parallel combination of a 10  $\mu$ F tantalum and a 0.1  $\mu$ F ceramic capacitor. This decoupling scheme reduces the noise spectral density of the reference.

Figure 3. Reference Decoupling Scheme

#### **External Reference**

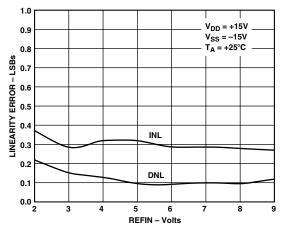

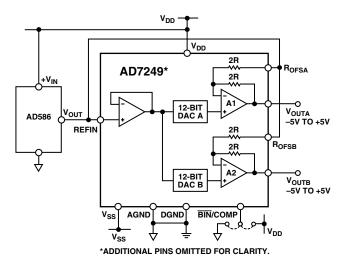

In some applications, the user may require a system reference or some other external reference to drive the AD7249. References such as the AD586 provide an ideal external reference source (See Figure 10). The REFIN voltage is internally buffered by a unity gain amplifier before being applied to the D/A converter. The D/A converter is scaled for a 5 V reference and the device is tested with 5 V applied to REFIN. Other reference voltages may be used with degraded performance. Figure 4 shows the degradation in linearity vs. REFIN.

Figure 4. Linearity vs. REFIN Voltage

#### **Op Amp Section**

The output of the voltage-mode D/A converter is buffered by a noninverting CMOS amplifier. The  $R_{OFS}$  input allows three output voltage ranges to be selected. The buffer amplifier is capable of developing +10 V across a 2 k $\Omega$  load to AGND.

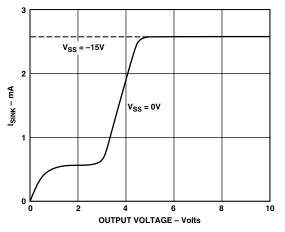

The output amplifier can be operated from a single +15 V supply by tying  $V_{SS} = 0$  V.

The amplifier can also be operated from dual supplies to allow an additional bipolar output range of -5 V to +5 V. Dual supplies are necessary for the bipolar output range but can also be used for the unipolar ranges to give faster settling time to voltages near 0 V, to allow full sink capability of 2.5 mA over the entire output range and to eliminate the effects of negative offsets on the transfer characteristic (outlined previously). A plot of the output sink capability of the amplifier is shown in Figure 5.

Figure 5. Amplifier Sink Current

Figure 6. Noise Spectral Density vs. Frequency

#### DIGITAL INTERFACE

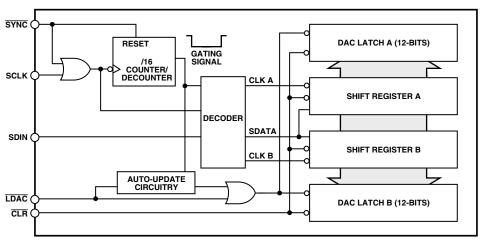

The AD7249 contains an input serial to parallel shift register and a DAC latch for both DAC A and DAC B. A simplified diagram of the input loading circuitry is shown in Figure 7. Serial data on the SDIN input is loaded to the input register under control of SYNC and SCLK. The SYNC input provides the frame synchronization signal which tells the AD7249 that valid serial data on the SDIN input will be available for the next 16 falling edges of SCLK. An internal counter/decoder circuit provides a low gating signal so that only 16 data bits are clocked into the input shift register. After 16 SCLK pulses the internal gating signal goes inactive (high) thus locking out any further clock pulses. Therefore either a continuous clock or a burst clock source may be used to clock in the data. The SYNC input is taken high after the complete 16-bit word is loaded in.

DAC selection is accomplished using the thirteenth bit (DB12) of the serial data input stream. A zero in DB12 will select DAC A while a one in this position selects DAC B. Although 16 bits of data are clocked into the input register, only 12 bits get transferred into the DAC latch. The relevant DAC latch is determined by the value of the thirteenth bit and the first three bits in the 16-bit stream are don't cares. Therefore, the data format is three don't cares followed by the DAC selection bit and the 12-bit data word with the LSB as the last bit in the serial stream.

There are two ways in which a DAC latches and hence the analog outputs may be updated. The status of the  $\overline{\text{LDAC}}$  input is examined after  $\overline{\text{SYNC}}$  is taken low. Depending on its status, one of two update modes are selected.

If  $\overline{\text{LDAC}} = 0$ , then the automatic update mode is selected. In this mode the DAC latch and analog output are updated automatically when the last bit in the serial data stream is clocked in. The update thus takes place on the sixteenth falling SCLK edge.

If  $\overline{\text{LDAC}} = 1$ , then the automatic update is disabled and both DAC latches are updated by taking  $\overline{\text{LDAC}}$  low any time after the 16-bit data transfer is complete. The update now occurs on the falling edge of  $\overline{\text{LDAC}}$ . Note that the  $\overline{\text{LDAC}}$  input must be taken back high again before the next data transfer is initiated. When a complete word is held in the shift register it may then be loaded into the DAC latch under control of  $\overline{\text{LDAC}}$ .

#### Clear Function (CLR)

The clear function clears the contents of the input shift register and loads both DAC latches with all 0s. It is activated by taking  $\overline{\text{CLR}}$  low. In all ranges except the Offset Binary bipolar range (-5 V to +5 V) the output voltage is reset to 0 V. In the offset binary bipolar range the output is set to -REFIN. The clear function is especially useful at power-up as it enables the output to be reset to a known state.

Figure 7. Simplified Loading Structure

Figure 8. Timing Diagram

#### TRANSFER FUNCTION

The internal scaling resistors provided on the AD7249 allow several output voltage ranges. The part can produce unipolar output ranges of 0 V to +5 V or 0 V to +10 V and a bipolar output range of  $\pm$ 5 V. Connections for the various ranges are outlined below. Since each DAC has its own R<sub>OFS</sub> input the two DACs can be set up for different output ranges.

#### Unipolar (0 V to +10 V) Configuration

The first of the configurations provides an output voltage range of 0 V to +10 V. This is achieved by connecting the output offset resistor  $R_{OFSA}$ ,  $R_{OFSB}$  (Pin 3, 16) to AGND. Natural Binary data format is selected by connecting  $\overline{BIN}/COMP$  (Pin 7) to DGND. In this configuration, the AD7249 can be operated using either single or dual supplies. Note that the V<sub>DD</sub> supply is

Figure 9. Unipolar (0 V to +10 V) Configuration

restricted to +15 V  $\pm$  10% for this range in order to maintain sufficient amplifier headroom. Dual supplies may be used to improve settling time and give increased current sink capability for the amplifier. Figure 9 shows the connection diagram for unipolar operation of the AD7249. Table I shows the digital code vs. analog output for this configuration.

#### Unipolar (0 V to +5 V) Configuration

The 0 V to +5 V output voltage range is achieved by tying R<sub>OFSA</sub> to V<sub>OUTA</sub> or R<sub>OFSB</sub> to V<sub>OUTB</sub>. Once again, the AD7249 can be operated using either single or dual supplies. The table for output voltage versus digital code is as in Table I, with 2REFIN replaced by REFIN. Note, for this range, 1 LSB = REFIN ×  $(2^{-12})$  = (REFIN/4096).

| Table I. | Unipolar Co | ode Table (0 | V to +10 V | Range) |

|----------|-------------|--------------|------------|--------|

|----------|-------------|--------------|------------|--------|

| Input Data Word              |     |                                                         |

|------------------------------|-----|---------------------------------------------------------|

| MSB                          | LSB | Analog Output, V <sub>OUT</sub>                         |

| XXXY 1111 11<br>XXXY 1000 00 |     | +2REFIN × (4095/4096)<br>+2REFIN × (2049/4096)          |

| XXXY 1000 00<br>XXXY 0111 11 |     | +2REFIN × (2048/4096) = +REFIN<br>+2REFIN × (2047/4096) |

| XXXY 0000 00<br>XXXY 0000 00 |     | +2REFIN × (1/4096)<br>0 V                               |

X = Don't Care.

Y = DAC Select Bit, 0 = DAC A, 1= DAC B.

Note: 1 LSB = 2REFIN/4096.

#### Bipolar (±5 V) Configuration

The bipolar configuration for the AD7249, which gives an output range of -5 V to +5 V, is achieved by connecting R<sub>OFSA</sub>, R<sub>OFSB</sub> to V<sub>REFIN</sub>. The AD7249 must be operated from dual supplies to achieve this output voltage range. Either offset binary or twos complement coding may be selected. Figure 10 shows the connection diagram for bipolar operation. An AD586 provides the reference voltage for the DAC but this could be provided by the on-chip reference by connecting REFOUT to REFIN.

**Bipolar Operation (Twos Complement Data Format)** The AD7249 is configured for twos complement data format by connecting BIN/COMP (Pin 7) high. The analog output vs. digital code is shown in Table II.

| Table II. Twos | <b>Complement</b> | <b>Bipolar</b> | Code Table | • |

|----------------|-------------------|----------------|------------|---|

|----------------|-------------------|----------------|------------|---|

| Input Data Word<br>MSB LSB | Analog Output, V <sub>OUT</sub> |

|----------------------------|---------------------------------|

| XXXY 0111 1111 1111        | +REFIN × (2047/2048)            |

| XXXY 0000 0000 0001        | +REFIN × (1/2048)               |

| XXXY 0000 0000 0000        | 0 V                             |

| XXXY 1111 1111 1111        | -REFIN × (1/2048)               |

| XXXY 1000 0000 0001        | -REFIN × (2047/2048)            |

| XXXY 1000 0000 0000        | -REFIN × (2048/2048) = -REFIN   |

X = Don't Care.

Y = DAC Select Bit, 0 = DAC A, 1 = DAC B.

Note: 1 LSB = REFIN/2048.

#### Bipolar Operation (Offset Binary Data Format)

The AD7249 is configured for Offset Binary data format by connecting  $\overline{\text{BIN}}/\text{COMP}$  (Pin 7) low. The analog output vs. digital code may be obtained by inverting the MSB in Table II.

#### **APPLYING THE AD7249**

Good printed circuit board layout is as important as the overall circuit design itself in achieving high speed converter performance. The AD7249 works on an LSB size of 2.44 mV for the unipolar 0 V to 10 V range and the bipolar  $\pm 5$  V range, when using the unipolar 0 V to 5 V range the LSB size is 1.22 mV. Therefore the designer must be conscious of minimizing noise in both the converter itself and in the surrounding circuitry. Switching mode power supplies are not recommended as switching spikes can feedthrough to the on-chip amplifier. Other causes of concern are ground loops and feedthrough from microprocessors. These are factors which influence any high performance converter, and proper printed circuit board layout which minimizes these effects is essential to obtain high performance.

#### LAYOUT HINTS

Ensure that the layout has the digital and analog tracks separated as much as possible. Take care not to run any digital track alongside an analog signal track. Establish a single point analog ground separate from the logic system ground. Place this star ground as close as possible to the AD7249. Connect all analog grounds to this star point and also connect the AD7249 DGND pin to this point. Do not connect any other digital grounds to this analog ground point. Low impedance analog and digital power supply common returns are essential for low noise operation of high performance converters. To accomplish this track widths should be kept a wide as possible and also the use of ground planes minimizes impedance paths and also guards the analog circuitry from digital noise.

#### NOISE

Keep the signal leads on the  $V_{OUTA}$  and  $V_{OUTB}$  signals and the signal return leads to AGND as short as possible to minimize noise coupling. In applications where this is not possible use a shielded cable between the DAC outputs and their destination. Reduce the ground circuit impedance as much as possible since any potential difference in grounds between the DAC and its destination device appears as an error voltage in series with the DAC output.

#### **Power Supply Decoupling**

To achieve optimum performance when using the AD7249, the  $V_{DD}$  and  $V_{SS}$  lines should be decoupled to AGND using 0.1  $\mu F$  capacitors. In noisy environments it is recommended that 10  $\mu F$  capacitors be connected in parallel with the 0.1  $\mu F$  capacitors.

#### MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD7249 is via a serial bus which uses standard protocol compatible with DSP processors and microcontrollers. The communications channel requires a three-wire interface consisting of a clock signal, a data signal and a synchronization signal. The AD7249 requires a 16-bit data word with data valid on the falling edge of SCLK. For all the interfaces, the DAC update may be done automatically when all the data is clocked in or it may be done under control of  $\overline{\text{LDAC}}$ .

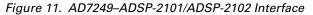

Figures 11 to 15 show the AD7249 configured for interfacing to a number of popular DSP processors and microcontrollers.

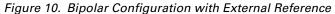

#### AD7249-ADSP-2101/ADSP-2102 Interface

Figure 11 shows a serial interface between the AD7249 and the ADSP-2101/ADSP-2102 DSP processor. The ADSP-2101/ ADSP-2102 contains two serial ports and either port may be used in the interface. The data transfer is initiated by  $\overline{TFS}$ going low. Data from the ADSP-2101/ADSP-2102 is clocked into the AD7249 on the falling edge of SCLK. DB12 of the 16-bit serial data stream selects the DAC to be updated. Both DACs can be updated by holding  $\overline{\text{LDAC}}$  high while performing two write cycles to the DAC. TFS must be taken high after each 16 bit write cycle.  $\overline{\text{LDAC}}$  is brought low at the end of the second cycle and both DAC outputs are updated together. In the interface shown the DAC is updated using an external timer which generates an  $\overline{\text{LDAC}}$  pulse. This could also be done using a control or decoded address line from the processor. Alternatively, if the  $\overline{\text{LDAC}}$  input is hardwired low the output update takes place automatically on the 16th falling edge of SCLK.

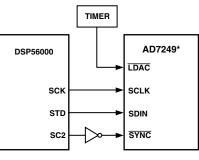

#### AD7249-DSP56000 Interface

A serial interface between the AD7249 and the DSP56000 is shown in Figure 12. The DSP56000 is configured for Normal Mode Asynchronous operation with Gated Clock. It is also set up for a 16-bit word with SCK and SC2 as outputs and the FSL control bit set to a "0." SCK is internally generated on the DSP56000 and applied to the AD7249 SCLK input. Data from the DSP56000 is valid on the falling edge of SCK. The SC2 output provides the framing pulse for valid data. This line must be inverted before being applied to the SYNC input of the AD7249.

\*ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 12. AD7249–DSP56000 Interface

In this interface an external  $\overline{\text{LDAC}}$  pulse generated from an external timer is used to update the outputs of the DACs. This update can also be produced using a bit programmable control line from the DSP56000.

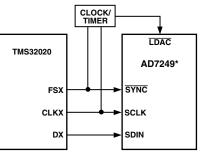

### AD7249-TMS32020 Interface

Figure 13 shows a serial interface between the AD7249 and the TMS32020 DSP processor. In this interface, the CLKX and FSX signals for the TMS32020 should be generated using external clock/timer circuitry. The FSX pin of the TMS32020 must be configured as an input. Data from the TMS32020 is valid on the falling edge of CLKX.

The clock/timer circuitry generates the  $\overline{\text{LDAC}}$  signal for the AD7249 to synchronize the update of the output with the serial transmission. Alternatively, the automatic update mode may be selected by connecting  $\overline{\text{LDAC}}$  to DGND.

\*ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 13. AD7249–TMS32020 Interface

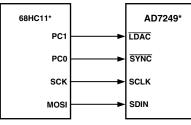

#### AD7249-68HC11 Interface

Figure 14 shows a serial interface between the AD7249 and the 68HC11 microcontroller. SCK of the 68HC11 drives SCLK of the AD7249 while the MOSI output drives the serial data line of the AD7249. The SYNC signal is derived from a port line (PC0 shown).

For correct operation of this interface, the 68HC11 should be configured such that its CPOL bit is a 0 and its CPHA bit is a 1. When data is to be transmitted to the part, PC0 is taken low. When the 68HC11 is configured like this, data on MOSI is valid on the falling edge of SCK. The 68HC11 transmits its serial data in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. To load data to the AD7249, PC0 is left low after the first eight bits are transferred and a second byte of data is then transferred serially to the AD7249. When the second serial transfer is complete, the PC0 line is taken high.

Figure 14 shows the  $\overline{\text{LDAC}}$  input of the AD7249 being driven from another bit programmable port line (PC1). As a result, both DACs can be updated simultaneously by taking  $\overline{\text{LDAC}}$ low after both DACs latches have updated.

\*ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 14. AD7249–68HC11 Interface

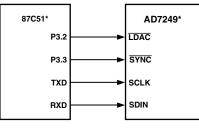

#### AD7249-87C51 Interface

A serial interface between the AD7249 and the 87C51 microcontroller is shown in Figure 15. TXD of the 87C51 drives SCLK of the AD7249 while RXD drives the serial data line of the part. The SYNC signal is derived from the port line P3.3 and the  $\overline{\text{LDAC}}$  line is driven port line P3.2.

The 87C51 provides the LSB of its SBUF register as the first bit in the serial data stream. Therefore, the user will have to ensure that the data in the SBUF register is arranged correctly so that the don't care bits are the first to be transmitted to the AD7249 and the last bit to be sent is the LSB of the word to be loaded to the AD7249. When data is to be transmitted to the part, P3.3 is taken low. Data on RXD is valid on the falling edge of TXD. The 87C51 transmits its serial data in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. To load data to the AD7249, P3.3 is left low after the first eight bits are transferred, and a second byte of data is then transferred serially to the AD7249 with DB12 used to select the appropriate DAC register. When the second serial transfer is complete, the P3.3 line is taken high and then taken low again to start the loading sequence to the second DAC (see timing diagram Figure 8).

Figure 15 shows the  $\overline{\text{LDAC}}$  input of the AD7249 driven from the bit programmable port line P3.2. As a result, both DAC outputs can be updated simultaneously by taking the  $\overline{\text{LDAC}}$ line low following the completion of the write cycle to the second DAC. Alternatively  $\overline{\text{LDAC}}$  could be hardwired low and the analog output will be updated on the sixteenth falling edge of TXD after the  $\overline{\text{SYNC}}$  signal for the DAC has gone low.

\*ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 15. AD7249-87C51 Interface

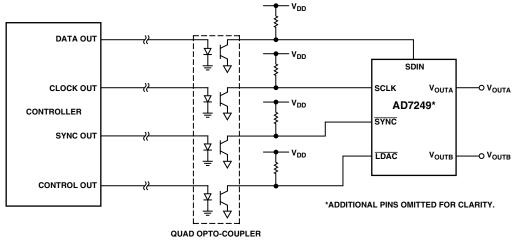

#### APPLICATIONS OPTO-ISOLATED INTERFACE

In many process control type applications it is necessary to provide an isolation barrier between the controller and the unit being controlled. Opto-isolators can provide voltage isolation in excess of 3 k $\Omega$ . The serial loading structure of the AD7249 makes it ideal for opto-isolated interfaces as the number of interface lines is kept to a minimum.

Figure 16 shows a 2-channel isolated interface using the AD7249.

The sequence of events to program the output channels is as follows.

- 1. Take the  $\overline{\text{SYNC}}$  line low.

- 2. Transmit the 16-bit word for DAC A (DB 12 of the 16-bit data word selects the DAC, DB12 = 0 to select DAC A) and bring the SYNC line high after the 16 bits have been transmitted.

- 3. Bring <u>SYNC</u> line low again and transmit 16 bits for DAC B, bring <u>SYNC</u> back high at end of transmission.

- 4. Pulse the  $\overline{\text{LDAC}}$  line low. This updates both output channels simultaneously on the falling edge of  $\overline{\text{LDAC}}$ .

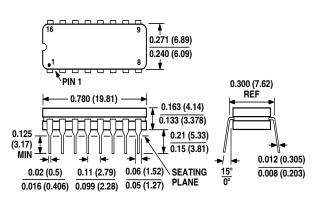

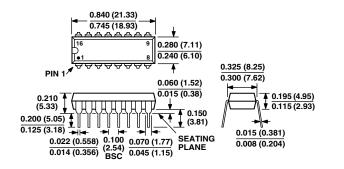

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

Plastic DIP (N-16)

Wide Body SOIC (R-16)

0.299 (7.60)

0.291 (7.40)

0.419 (10.65)

0.404 (10.26)

0.007 (0.18)

0.364 (9.246) 0.344 (8.738)

0.045 (1.15)

0.020 (0.50)

8° 0°

0.413 (10.50)

0.348 (10.10)

→ ← 0.050 (1.27) BSC

0.107 (2.72) 0.089 (2.26)

0.018 (0.46) 0.014 (0.36) SEATING PLANE 0.015 (0.38) 0.007 (0.18)

Ħ

16

⋪╢

₽Ū

0.010 (0.25)

0.004 (0.10)

PIN 1